同名の表題でhttp://blogs.yahoo.co.jp/andre_5814/57172309.html としてUPした記事が、該当のカテゴリの一覧に反映されない不具合があるのでlinkを張ります

2016年02月

蝙蝠と無線機

無線機の自作の参考にするのに、メーカー製無線機の資料を検索するのですが、メーカー側は、最近あまり細かい手の内を明かすことが少なくなってきたような気がします。(ページ数だけは、やたら多いのですが)

たぶん、つっこみされることが、お気に召さないのでしょう。

ケンウッドのTS-990ですが、送信の系統図を見ると第一IFは24kHzのようです。

マイクからの音声を48kHzのレートでAD変換、DSPでphase_shiftと24kHzのデジタルI/Q変調後、DA変換していますね。

24kHzのSSBは人間の耳には聞こえないでしょうが、蝙蝠なら聞こえるかもしれません。

TS-990のAD変換からDA変換までの回路をスルーして、蝙蝠の発する超音波をIF段に直接入力すると、目的周波数が送信できそうですね。

蝙蝠さんは、たぶん無線従事者免許を持っていないだろうから法的に無理かな?

何を言いたいかというと、今時の大方の無線機で、デジタル処理しているのは、低周波信号の領域だけだということです。

高周波の領域にまったく貢献していないというわけではないのでしょうが、少なくても信号処理の対象にしているのは、低周波だけですよね。

24kHzの信号から、周波数変換するわけですから、目的周波数から48kHz離れたところにイメージ・スプリアスが出る。

これを切るために帯域幅が6kHz程度のクリスタル・フィルタなどを通すというか、クリスタル・フィルタを使わざるを得ないのです。

これってPSN方式ではなくて、フィルター方式ではないでしょうか。

フィルターの群遅延特性や通過帯域内のリップルの問題は、どうなったのかな、DSPを使う大義名分は何だったのですか。

やってることは、ウン万円のカーオーディオ装置やカラオケマシンと変わらないのでは?

買ってきたままの無線機では、いい音がしないので内蔵のグライコを調整したりする楽しみが増えたのでしょうが、高価な大人のおもちゃと感じているのは私だけでしょうか

さて本題に戻って

Weaver式SSB 1次変調装置 v2を作っています。

1次変調装置では、過去にデジタル・フィルタDF1704を使って、サンプルレートを768kHzまで上げた回路を作ったのですが、このICが入手困難になってきたので、768kHz対応のサンプル・レート・コンバータ(SRC)の代替品を物色していました。

昨年、旭化成エレクトロニクスより32bit/768kHz対応のSRC AK4137が発表されました。

この会社の製品は、先のケンウッドのTS-990あたりでよく使われているのですが、TIの製品などに比べて入手が楽ではないという印象がありました。

そんな中 「お気楽オーディオ」さんのサイトを検索していたら、DIGIKEYから入手できることがわかったので、2個購入しました。

1個目は、1次変調装置の最終段に据えて、サンプルレートを768kHzに上げることに使います。

2個目は、別の基板になりますが、192kHz/24bitのPCM信号を12.288MHz/1bitのPDM(DSD)信号の変換に使う予定です。

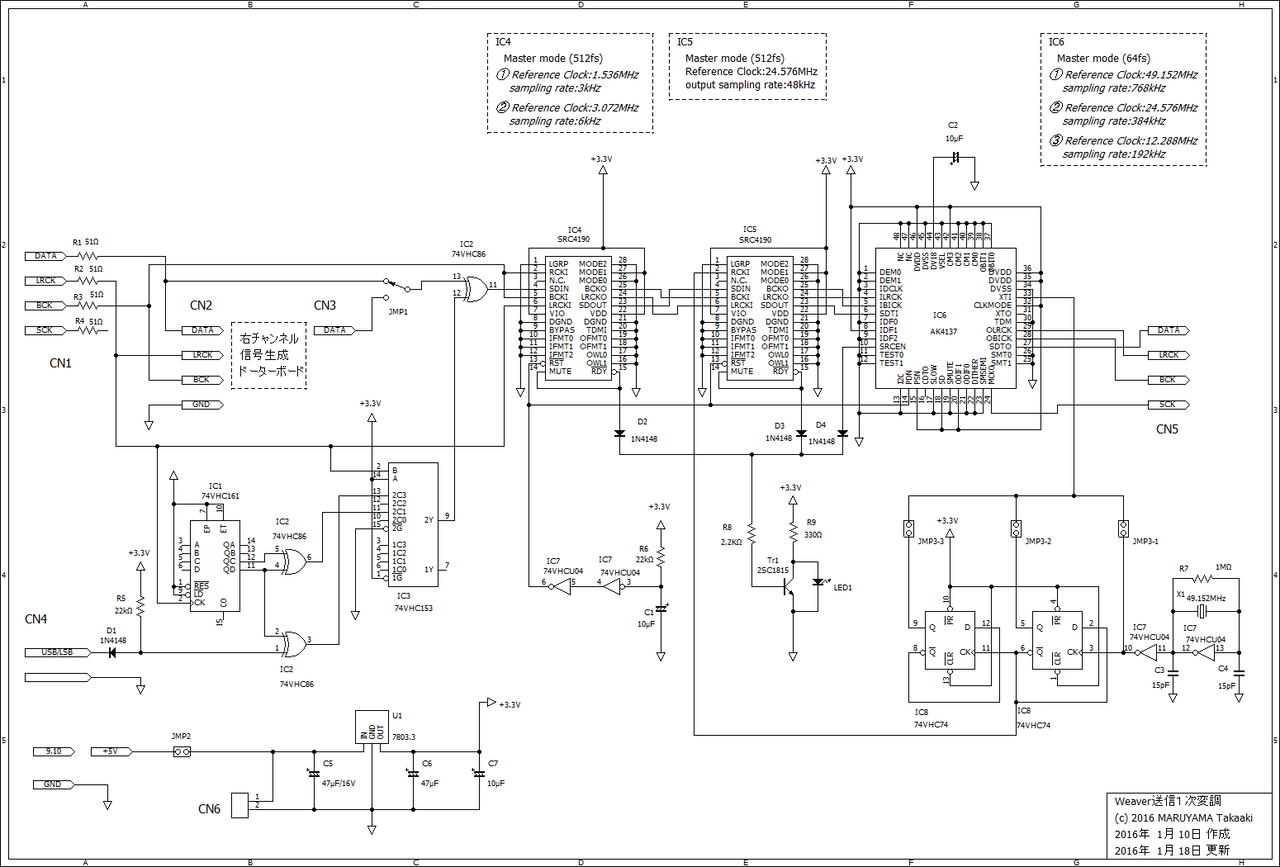

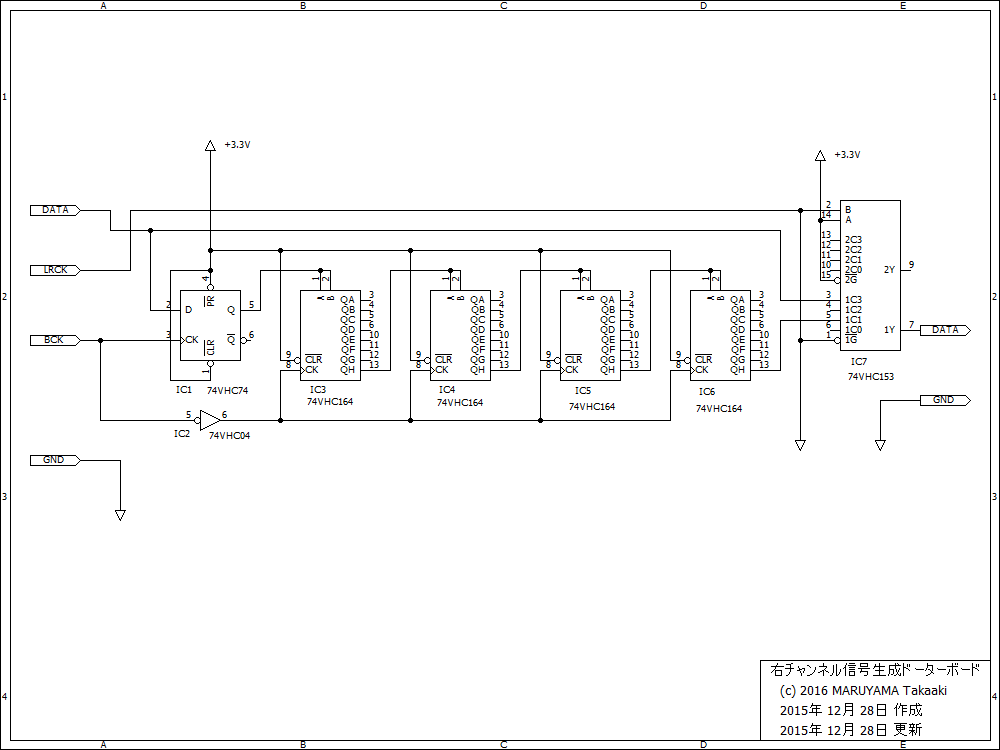

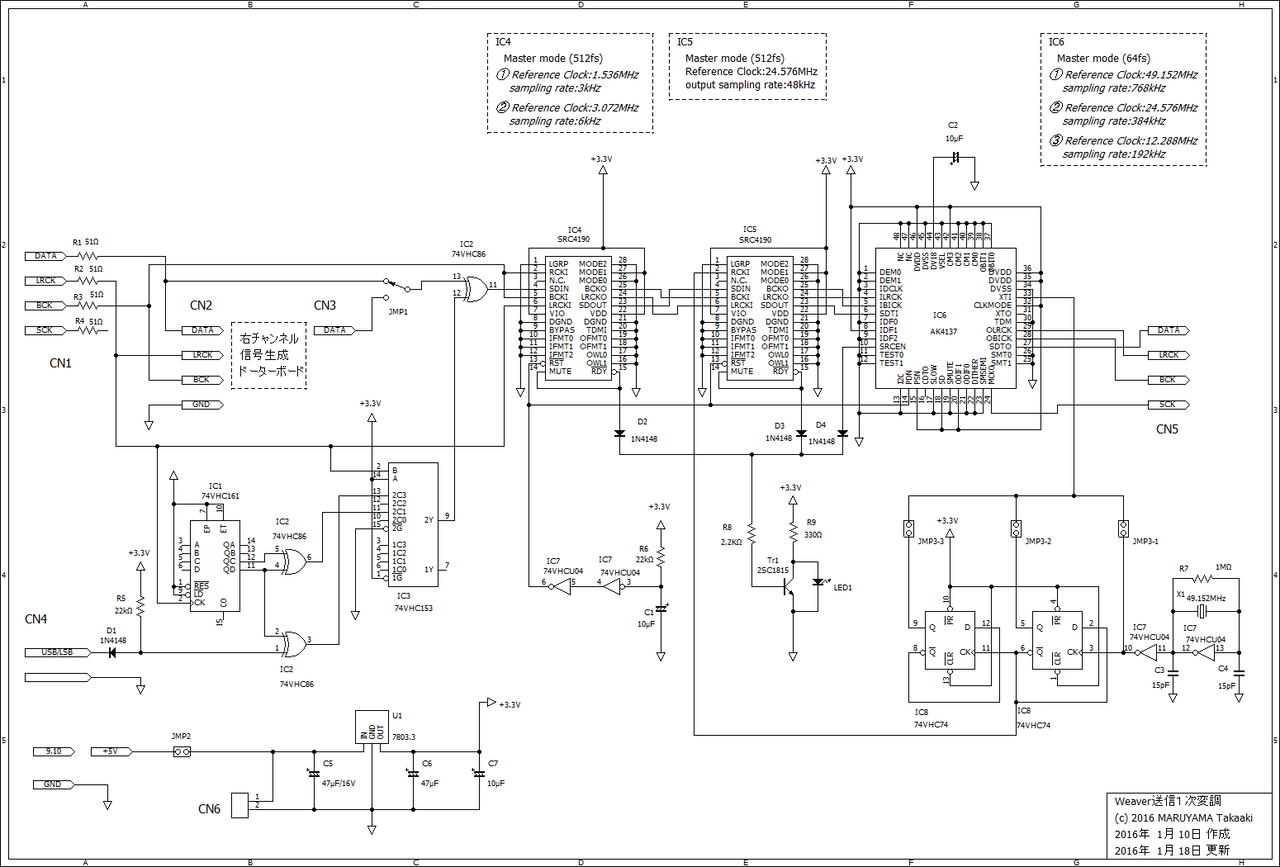

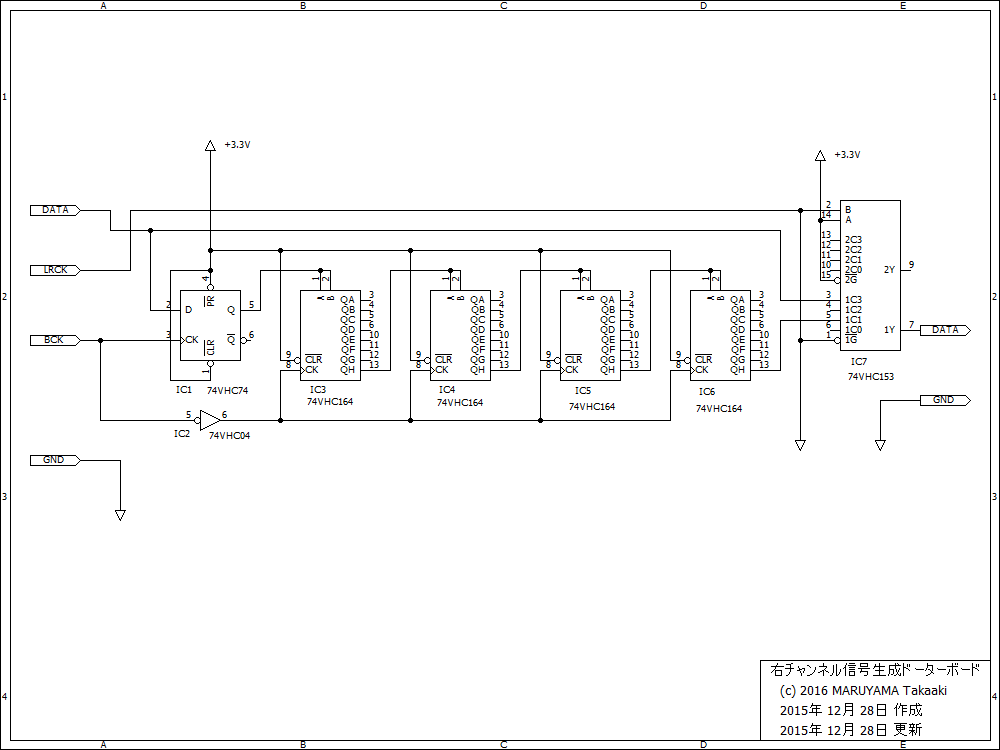

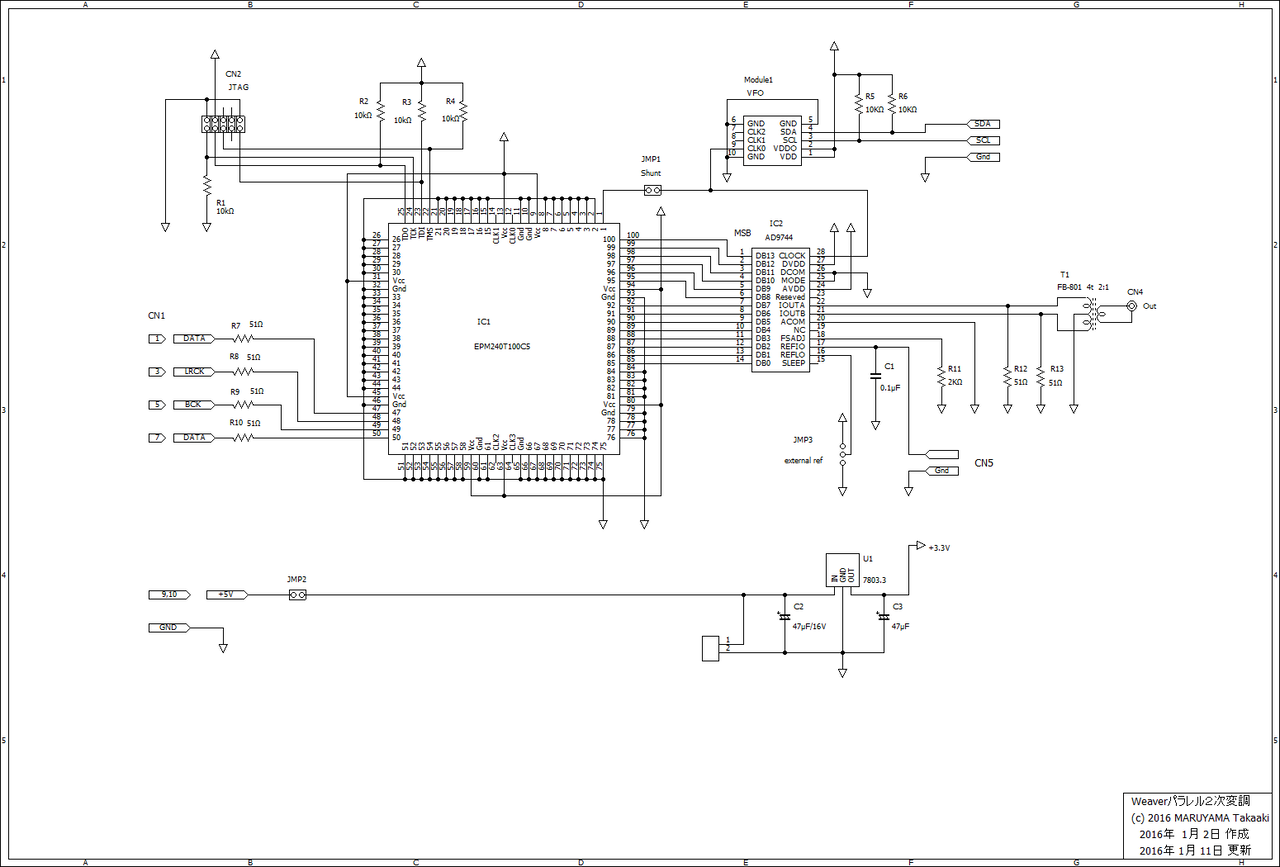

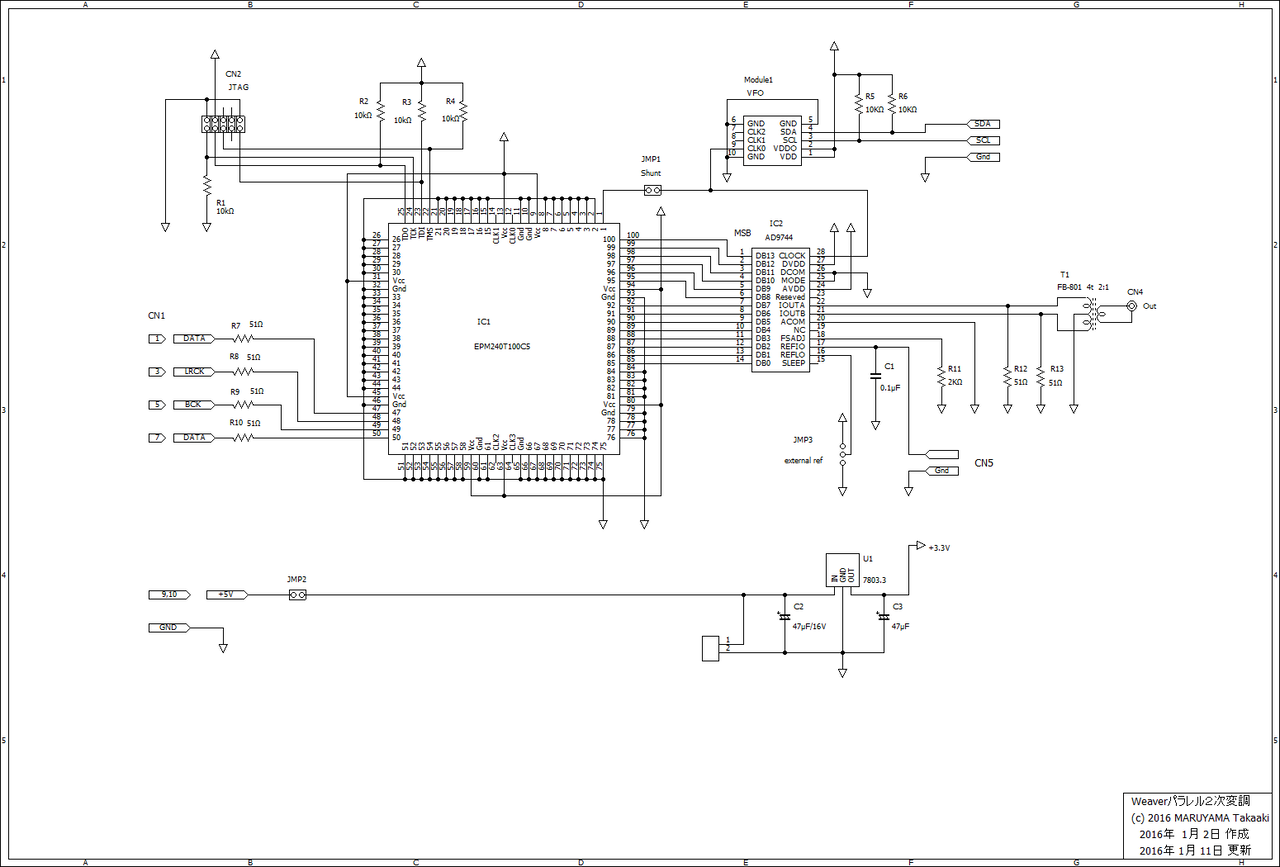

【1次変調装置の回路図】

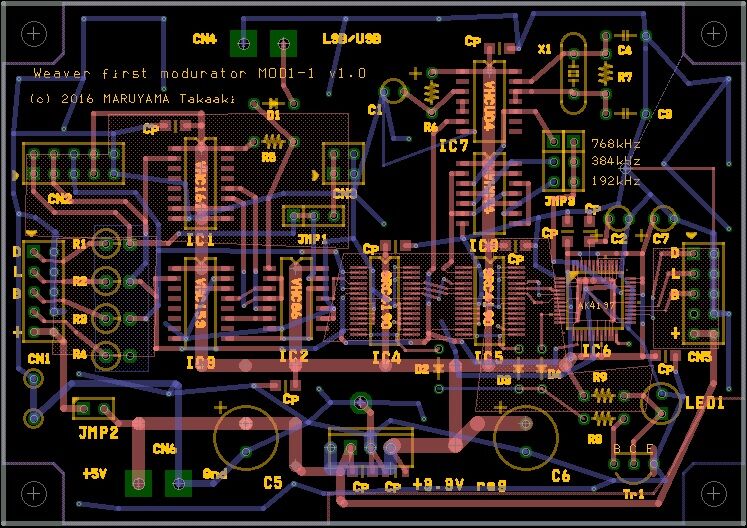

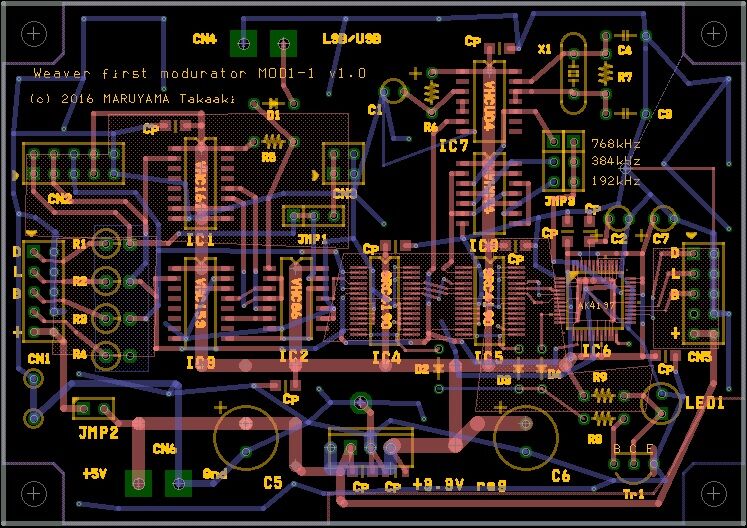

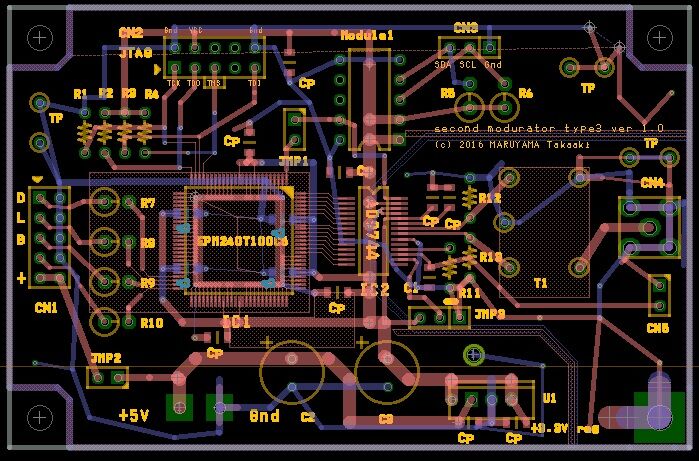

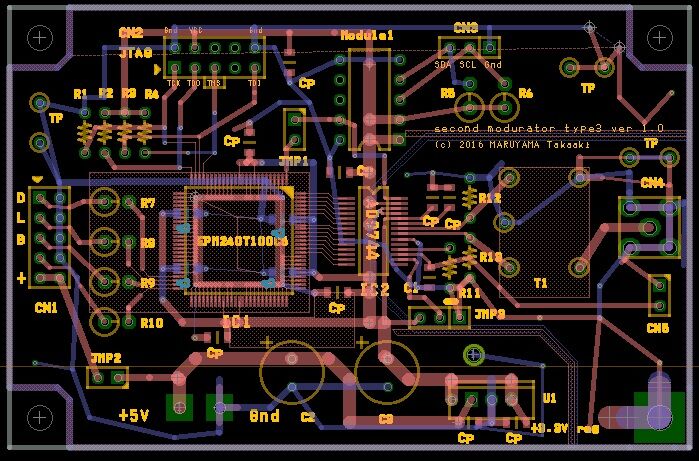

【基板のイメージ】

動作は、以前に作った基板http://blogs.yahoo.co.jp/andre_5814/57046538.html のUNIT2と、ほとんど同じですが、出力信号がDF1704の独特の4線式Formatから64bit/Frameの一般的な3線式Formatに変更になったことくらいです。

がんばってサンプル・レートを上げているのは、イメージ・スプリアスを目的周波数から離したいためです。

メーカー製の無線機のIF周波数が3桁kHz台になるまでに、あと数年かかるでしょうね。

ご訪問ありがとうございました。

たぶん、つっこみされることが、お気に召さないのでしょう。

ケンウッドのTS-990ですが、送信の系統図を見ると第一IFは24kHzのようです。

マイクからの音声を48kHzのレートでAD変換、DSPでphase_shiftと24kHzのデジタルI/Q変調後、DA変換していますね。

24kHzのSSBは人間の耳には聞こえないでしょうが、蝙蝠なら聞こえるかもしれません。

TS-990のAD変換からDA変換までの回路をスルーして、蝙蝠の発する超音波をIF段に直接入力すると、目的周波数が送信できそうですね。

蝙蝠さんは、たぶん無線従事者免許を持っていないだろうから法的に無理かな?

何を言いたいかというと、今時の大方の無線機で、デジタル処理しているのは、低周波信号の領域だけだということです。

高周波の領域にまったく貢献していないというわけではないのでしょうが、少なくても信号処理の対象にしているのは、低周波だけですよね。

24kHzの信号から、周波数変換するわけですから、目的周波数から48kHz離れたところにイメージ・スプリアスが出る。

これを切るために帯域幅が6kHz程度のクリスタル・フィルタなどを通すというか、クリスタル・フィルタを使わざるを得ないのです。

これってPSN方式ではなくて、フィルター方式ではないでしょうか。

フィルターの群遅延特性や通過帯域内のリップルの問題は、どうなったのかな、DSPを使う大義名分は何だったのですか。

メリットといえば音声の低域を安心して出せることぐらいではないですか?

ベースバンドのスペクトラムを、たった24kHz持ち上げるため、DSPを使って、これを殊更大げさに宣伝していませんかね。やってることは、ウン万円のカーオーディオ装置やカラオケマシンと変わらないのでは?

買ってきたままの無線機では、いい音がしないので内蔵のグライコを調整したりする楽しみが増えたのでしょうが、高価な大人のおもちゃと感じているのは私だけでしょうか

さて本題に戻って

Weaver式SSB 1次変調装置 v2を作っています。

1次変調装置では、過去にデジタル・フィルタDF1704を使って、サンプルレートを768kHzまで上げた回路を作ったのですが、このICが入手困難になってきたので、768kHz対応のサンプル・レート・コンバータ(SRC)の代替品を物色していました。

昨年、旭化成エレクトロニクスより32bit/768kHz対応のSRC AK4137が発表されました。

この会社の製品は、先のケンウッドのTS-990あたりでよく使われているのですが、TIの製品などに比べて入手が楽ではないという印象がありました。

そんな中 「お気楽オーディオ」さんのサイトを検索していたら、DIGIKEYから入手できることがわかったので、2個購入しました。

1個目は、1次変調装置の最終段に据えて、サンプルレートを768kHzに上げることに使います。

2個目は、別の基板になりますが、192kHz/24bitのPCM信号を12.288MHz/1bitのPDM(DSD)信号の変換に使う予定です。

【1次変調装置の回路図】

【基板のイメージ】

動作は、以前に作った基板http://blogs.yahoo.co.jp/andre_5814/57046538.html のUNIT2と、ほとんど同じですが、出力信号がDF1704の独特の4線式Formatから64bit/Frameの一般的な3線式Formatに変更になったことくらいです。

がんばってサンプル・レートを上げているのは、イメージ・スプリアスを目的周波数から離したいためです。

メーカー製の無線機のIF周波数が3桁kHz台になるまでに、あと数年かかるでしょうね。

ご訪問ありがとうございました。

Weaver式SSB パラレル2次変調装置 v3 (2)

続きです。

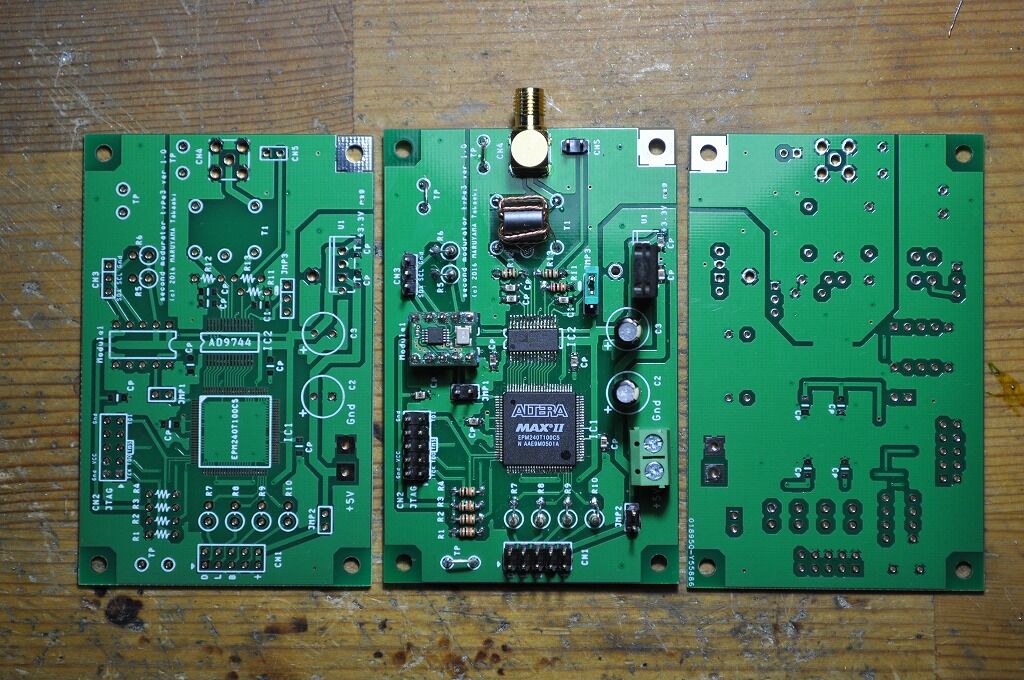

すべての部品をはんだ付けして、JTAGの端子からコンパイル結果をCPLDに無事書き込みできました。

テストは、1次変調基板が用意できるまで、お預けです。

クロック・モジュールの単体試験が先かな?

ご訪問有難うございました。

すべての部品をはんだ付けして、JTAGの端子からコンパイル結果をCPLDに無事書き込みできました。

テストは、1次変調基板が用意できるまで、お預けです。

クロック・モジュールの単体試験が先かな?

ご訪問有難うございました。

Weaver式SSB パラレル2次変調装置 v3 (1)

デジタル・オーディオ用のICなどを使用して無線機を作っています。

表題にあるパラレル2次変調装置は、今までは、http://blogs.yahoo.co.jp/andre_5814/57078875.html などのように、ユニバーサル基板と、トラ技の付録のCPLD基板などで構成していたのですが、以下の理由により、専用基板でリニューアルすることにしました。

1) トラ技の基板などでは、CPLDから本体基板のPinの配線割り付けが二重手間になる。

2) ベタアースを作りにくいので、高周波向きではない。

3) 再現性に欠け、美しくない。

などです。

幸いにして、トラ技の付録のCPLDと同じ「EPM240T100C5」と、ファミリーの「EPM570T100C5」の単体ICが、ある程度の数まとまって入手できました。

ロジックエレメント数は、前者が240、後者が570です。

正規のルートで入手すると、前者が@1,000円、後者が@2,000円程度ですが、余剰品なのか、格安に入手できました。

パッケージは両者とも100PinのQFPで、ピンの間隔は0.5mmです。

回路図と、基板のイメージです。

EPM240T100C5のデータシートを参照して回路を起こし、基板を設計したのですが、大失敗をしました。

ロジックエレメント数に関係なく、ICのパッケージが同じであればPinアサインが同じだとの思い込みで、EPM570T100C5とDACを基板にはんだ付けしました。

ところが、電源ラインとアース間がゼロΩ!…

よく調べたら、EPM570T100C5の方が、電源端子が数本多かったのでした、これらをアースに接続してしまったのです。

しょうがないので、基板ごとフライパンの上で焙ってICを外したのですが、基板とCPLDをオシャカにしてしまいました。

基板やCPLDに予備があったので、実験を続けることができましたが、不覚です。

ICメーカーのALTERAさん、ごめんなさいです。

【動作概要】

1) CN1よりPCM信号を入力、Formatは24Bit左詰め64Bit/Frame又はDF1704などVHDLで切替

2) CPLDでシリアル信号をパラレルに変換、I/Q変調をおこなってDACに送出

3) Module1は、Si5351を使ったクロックモジュール、目的周波数の4倍を発生

【その他】

覚悟はしていたのですが、ICのはんだ付けが大変です。

DACのAD9744は、TSSOPです。

足のピッチは0.65mmですが、これでもCPLDの足ピッチに比べて大幅に広く感じました。

CPLDは100Pinもあるのですが、実質使っているピンは20本程度で、残りはすべてアースに接続しています。

これらは隣同士がショートしていても、気にしないことにしました。

Module1は、ArduinoなどからI2Cで制御する予定です。

DDSと同様な使い方ができるようですが、PLL方式らしいです。@900円

続く

表題にあるパラレル2次変調装置は、今までは、http://blogs.yahoo.co.jp/andre_5814/57078875.html などのように、ユニバーサル基板と、トラ技の付録のCPLD基板などで構成していたのですが、以下の理由により、専用基板でリニューアルすることにしました。

1) トラ技の基板などでは、CPLDから本体基板のPinの配線割り付けが二重手間になる。

2) ベタアースを作りにくいので、高周波向きではない。

3) 再現性に欠け、美しくない。

などです。

幸いにして、トラ技の付録のCPLDと同じ「EPM240T100C5」と、ファミリーの「EPM570T100C5」の単体ICが、ある程度の数まとまって入手できました。

ロジックエレメント数は、前者が240、後者が570です。

正規のルートで入手すると、前者が@1,000円、後者が@2,000円程度ですが、余剰品なのか、格安に入手できました。

パッケージは両者とも100PinのQFPで、ピンの間隔は0.5mmです。

回路図と、基板のイメージです。

EPM240T100C5のデータシートを参照して回路を起こし、基板を設計したのですが、大失敗をしました。

ロジックエレメント数に関係なく、ICのパッケージが同じであればPinアサインが同じだとの思い込みで、EPM570T100C5とDACを基板にはんだ付けしました。

ところが、電源ラインとアース間がゼロΩ!…

よく調べたら、EPM570T100C5の方が、電源端子が数本多かったのでした、これらをアースに接続してしまったのです。

しょうがないので、基板ごとフライパンの上で焙ってICを外したのですが、基板とCPLDをオシャカにしてしまいました。

基板やCPLDに予備があったので、実験を続けることができましたが、不覚です。

ICメーカーのALTERAさん、ごめんなさいです。

【動作概要】

1) CN1よりPCM信号を入力、Formatは24Bit左詰め64Bit/Frame又はDF1704などVHDLで切替

2) CPLDでシリアル信号をパラレルに変換、I/Q変調をおこなってDACに送出

3) Module1は、Si5351を使ったクロックモジュール、目的周波数の4倍を発生

【その他】

覚悟はしていたのですが、ICのはんだ付けが大変です。

DACのAD9744は、TSSOPです。

足のピッチは0.65mmですが、これでもCPLDの足ピッチに比べて大幅に広く感じました。

CPLDは100Pinもあるのですが、実質使っているピンは20本程度で、残りはすべてアースに接続しています。

これらは隣同士がショートしていても、気にしないことにしました。

Module1は、ArduinoなどからI2Cで制御する予定です。

DDSと同様な使い方ができるようですが、PLL方式らしいです。@900円

続く